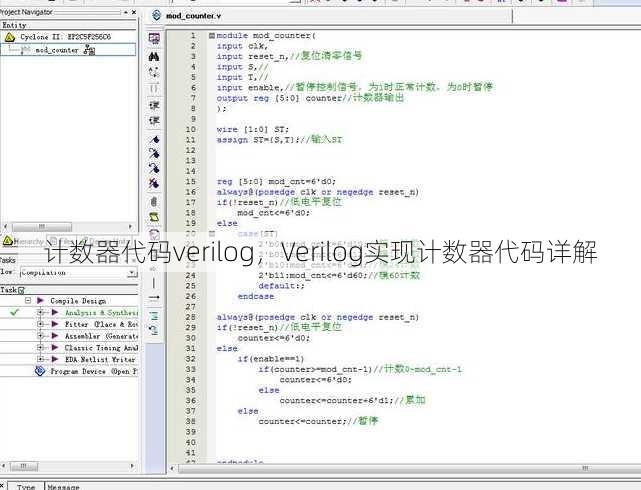

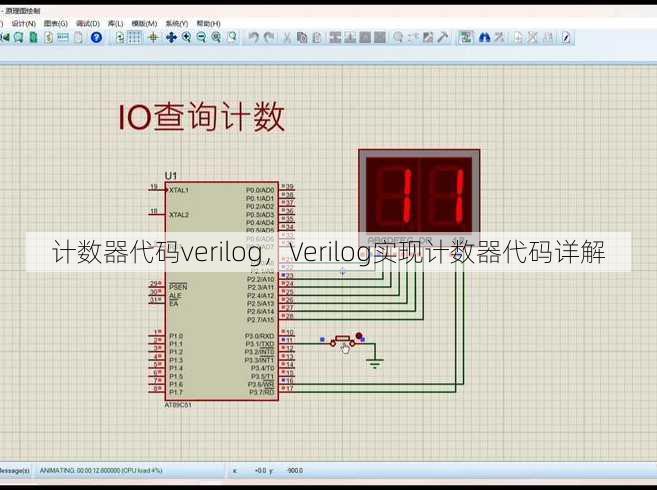

计数器代码verilog,Verilog实现计数器代码详解

计数器代码在Verilog中通常用于实现数字电路中的计数功能,以下是一个简化的Verilog计数器代码摘要:,```verilog,module counter (, input clk, // 时钟信号, input reset, // 复位信号, output [3:0] count // 4位计数输出,);,reg [3:0] count_reg;,always @(posedge clk or posedge reset) begin, if (reset), count_reg

嗨,我最近在学习Verilog,遇到了一个计数器设计的问题,我想知道如何用Verilog编写一个简单的4位二进制计数器,它能够从0计数到15,然后重置回到0,有没有高手能给我一个基本的代码示例呢?

一:计数器基础

计数器定义 计数器是一种数字电路,用于记录事件发生的次数,在Verilog中,计数器通常由一系列触发器组成,这些触发器按照一定的逻辑关系进行翻转。

触发器选择 在Verilog中,可以选择不同的触发器类型,如上升沿触发和下降沿触发,对于计数器,通常使用上升沿触发的D触发器。

计数器类型 计数器可以分为同步计数器和异步计数器,同步计数器所有触发器的时钟信号是同步的,而异步计数器则不同步,对于大多数应用,同步计数器更为常见。

二:Verilog计数器代码

代码结构 以下是一个简单的4位同步上升沿计数器的Verilog代码示例:

module counter_4bit (

input clk, // 时钟信号

input reset, // 异步复位信号

output reg [3:0] q // 4位输出

);

always @(posedge clk or posedge reset) begin

if (reset)

q <= 4'b0000; // 当复位信号为高时,计数器重置为0

else

q <= q + 1'b1; // 否则,计数器在时钟上升沿递增

end

endmodule

时钟信号

clk是计数器的时钟信号,它决定了计数器的计数速率。

复位信号

reset是异步复位信号,用于将计数器的值立即重置为0。

输出

q是4位输出,表示计数器的当前值。

三:计数器应用

应用场景 计数器在数字电路中应用广泛,如频率测量、定时器、序列发生器等。

优点 使用Verilog设计计数器可以方便地进行仿真和验证,同时易于集成到更大的系统中。

缺点 计数器设计需要考虑时钟频率、复位逻辑等因素,设计不当可能导致计数错误。

四:计数器扩展

扩展位数

要设计一个更大的计数器,只需增加输出位数即可,要设计一个16位计数器,只需将输出从reg [3:0]改为reg [15:0]。

同步扩展 同步扩展意味着所有触发器的时钟信号是同步的,这可以通过增加更多的触发器和逻辑门来实现。

异步扩展 异步扩展意味着触发器的时钟信号不是同步的,这通常更复杂,需要仔细设计。

五:计数器仿真

仿真工具 可以使用如ModelSim、Vivado等仿真工具对计数器进行仿真。

仿真步骤 编写测试模块,初始化计数器,然后模拟时钟信号和复位信号,观察输出结果。

仿真验证 通过仿真验证计数器是否按预期工作,确保没有设计错误。 相信你已经对Verilog计数器有了基本的了解,在实际应用中,根据具体需求调整计数器的设计和功能。

其他相关扩展阅读资料参考文献:

Verilog计数器代码详解

计数器是数字系统中常见的组成部分,用于记录事件发生的次数或测量时间间隔,在Verilog硬件描述语言中,计数器广泛应用于数字电路的设计和实现,本文将地讲解Verilog计数器代码的相关要点。

一:计数器的类型

- 递增计数器:最基本的计数器,每次触发输入信号时,计数值递增。

- 递减计数器:与递增计数器相反,每次触发时计数值递减。

- 模数计数器:当计数值达到预设模数时,自动回零重新开始计数。

二:计数器的结构

- 寄存器结构:使用寄存器存储计数值,通过控制信号更新寄存器的值。

- 逻辑结构:通过逻辑门电路实现计数逻辑,适用于简单的计数器设计。

- 状态机结构:利用状态转移实现计数功能,适用于复杂的计数器设计。

三:Verilog实现计数器代码示例

以下是一个简单的递增计数器的Verilog代码示例:

module Counter(input wire clk, reset, enable, output reg [3:0] count);

always @(posedge clk or posedge reset) begin

if (reset) count <= 4'b0000; //复位计数值为0

else if (enable) count <= count + 4'b0001; //每次触发时计数递增

end

endmodule

解释:这段代码定义了一个简单的计数器模块,具有时钟输入clk、复位输入reset和使能输入enable,当使能信号有效时,计数器在每个时钟上升沿递增,复位信号用于将计数器清零,这是一个基本的递增计数器的实现方式,在实际应用中,可以根据需求调整计数器的逻辑和功能。 五、四:计数器的优化与应用场景

在数字系统中,计数器经常需要根据实际需求进行优化和改进,使用流水线技术提高计数速度,使用中断机制实现异步计数等,计数器广泛应用于定时器、频率分频、状态机等场景,熟悉这些应用场景有助于更好地理解和设计计数器电路,掌握Verilog计数器代码对于数字系统设计至关重要,通过学习和实践,可以更加灵活地运用计数器实现各种复杂的数字系统应用。

“计数器代码verilog,Verilog实现计数器代码详解” 的相关文章

beanfun注册,Beanfun官方注册指南

Beanfun注册流程简要的介绍:用户需访问Beanfun官方网站,填写个人资料,包括姓名、邮箱等,并设置密码,随后,通过邮箱验证激活账户,注册成功后,用户可享受Beanfun提供的游戏、娱乐等服务,请注意保护个人信息,确保账户安全。beanfun注册全攻略:轻松开启游戏之旅 真实用户解答: 大...

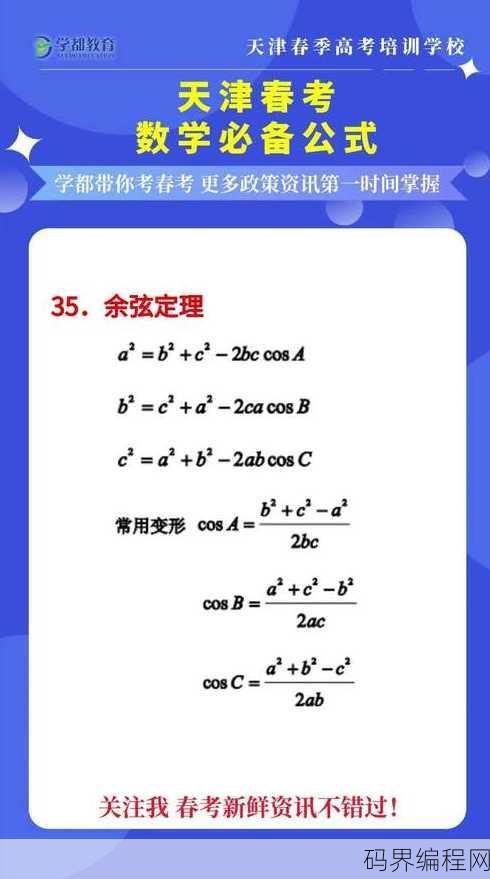

余弦定理,余弦定理在几何中的应用解析

余弦定理是三角形中一条重要的数学定理,用于计算三角形各边长度与角之间的关系,该定理表明,在任意三角形中,一个角的余弦值等于其他两边的平方和减去第三边平方,再除以这两边乘积的两倍,余弦定理广泛应用于几何证明、工程计算以及物理学等领域,是解决三角形边角问题的重要工具。 嗨,我在学习余弦定理的时候遇到了...

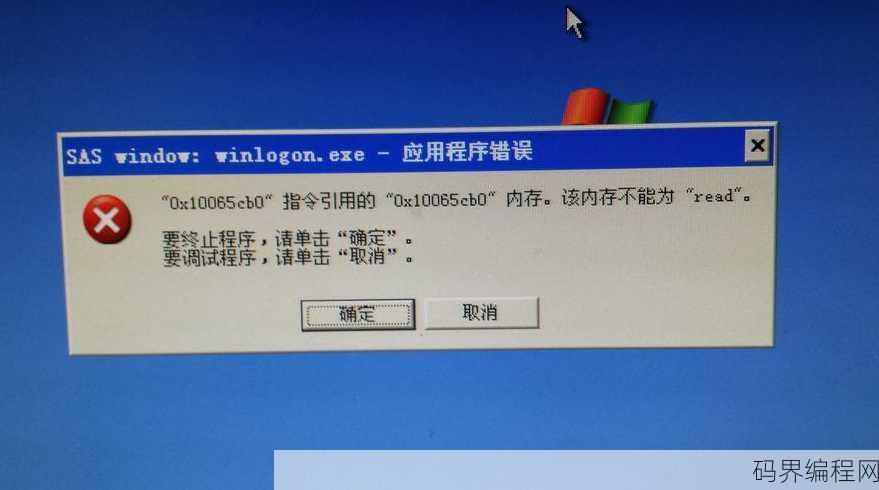

电脑无限弹窗代码,破解电脑无限弹窗困扰,代码揭秘

电脑无限弹窗代码通常指的是一种恶意软件或病毒编写的技术,它能够让电脑屏幕上不断弹出大量广告或信息窗口,这种代码通常通过恶意软件安装到用户电脑上,一旦激活,就会自动运行并不断弹出窗口,干扰用户正常使用电脑,要解决这个问题,需要使用杀毒软件进行检测和清除,并确保电脑操作系统和软件都是最新版本,以防止类似...

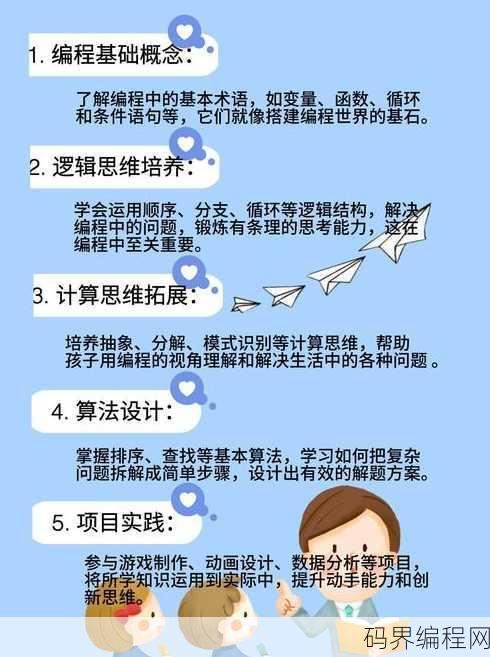

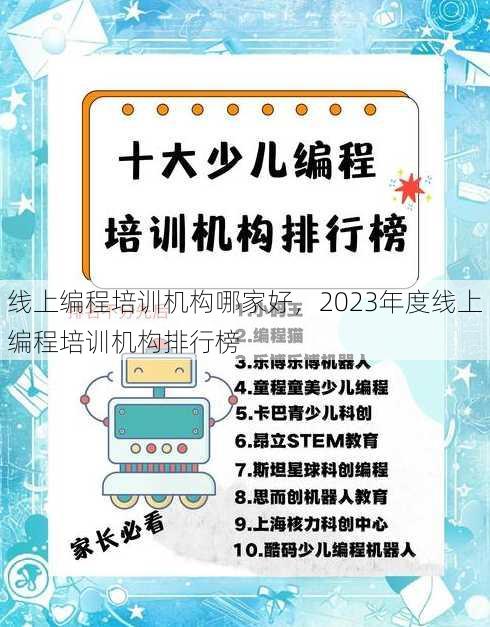

少儿编程主要学的是什么,少儿编程核心知识解析

少儿编程主要学习计算机科学的基本概念,包括逻辑思维、算法设计、编程语言基础、图形化编程以及实际项目开发,课程内容通常包括编程语言如Scratch、Python等,通过游戏化、互动式教学,培养孩子的创新能力和解决问题的能力,同时提升他们对数字世界的理解和应用技能。少儿编程主要学的是什么? 用户解答:...

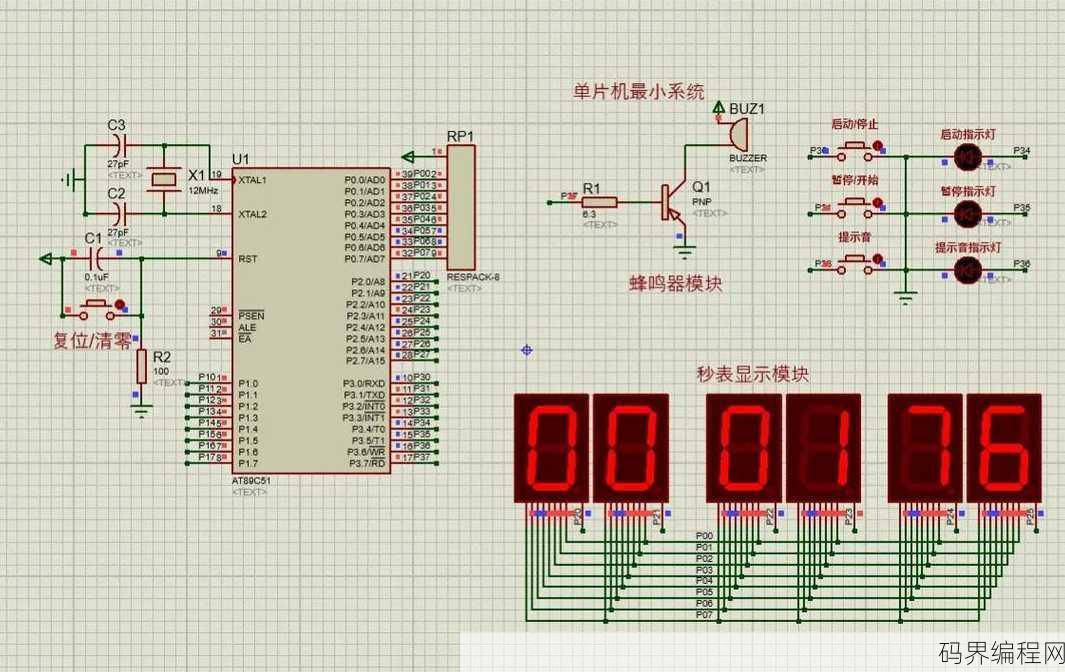

单片机编程是什么,单片机编程入门指南

单片机编程是指使用特定编程语言和工具对单片机进行编程的过程,单片机是一种集成了微处理器、存储器和输入输出接口的微型计算机,编程目的在于让单片机执行特定的任务,如控制家用电器、工业自动化设备等,程序员需要编写代码,使单片机能够接收输入、处理数据和输出结果,这个过程涉及了解单片机的硬件特性、选择合适的编...

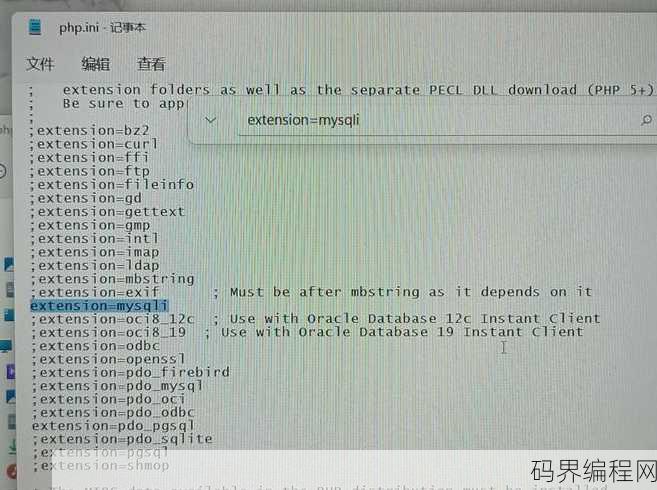

iis运行php,IIS支持PHP配置与运行指南

IIS(Internet Information Services)是微软推出的一种Web服务器软件,它支持多种服务器端脚本语言,包括PHP,通过配置IIS,可以使其支持PHP运行,从而在Windows服务器上实现PHP应用程序的部署,配置过程中,需要安装PHP运行环境,并配置IIS以识别和执行PH...